Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering The Department of Computer and Information Science

### TDT4160 Computer, Fundamentals (Datamaskiner grunnkurs) Exam

10. DECEMBER, 2008, 09:00-13:00

#### **Contact:**

Gunnar Tufte 73590356

#### **Examination support materials:**

D.

No written and handwritten examination support materials are permitted. A specified, simple calculator is permitted.

#### Language:

English

## Question 1: Digital Logic Level (20% (10% on A, 5% on B and C))

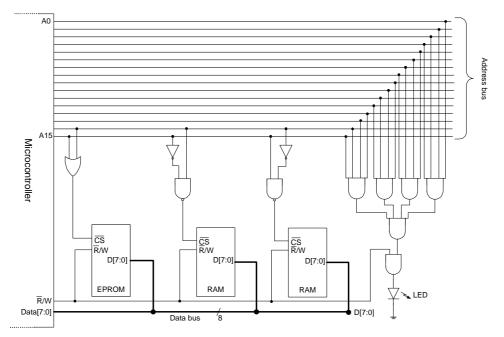

a. In Figure 1 EPROM, RAM and a light emitting diode (LED) share a common bus. What are the memory address ranges for the devices? EPROM and RAM uses an active low (logic "0") Chip Select (CS) signal.

Figur 1: Address decoding.

- b. Is it possible to extend the system with 16kB (16384 bytes) of RAM? Explain.

- c. When is the LED lit?

### Question 2: Microarchitecture and microinstructions (20% (5% on a and b; 10% on c))

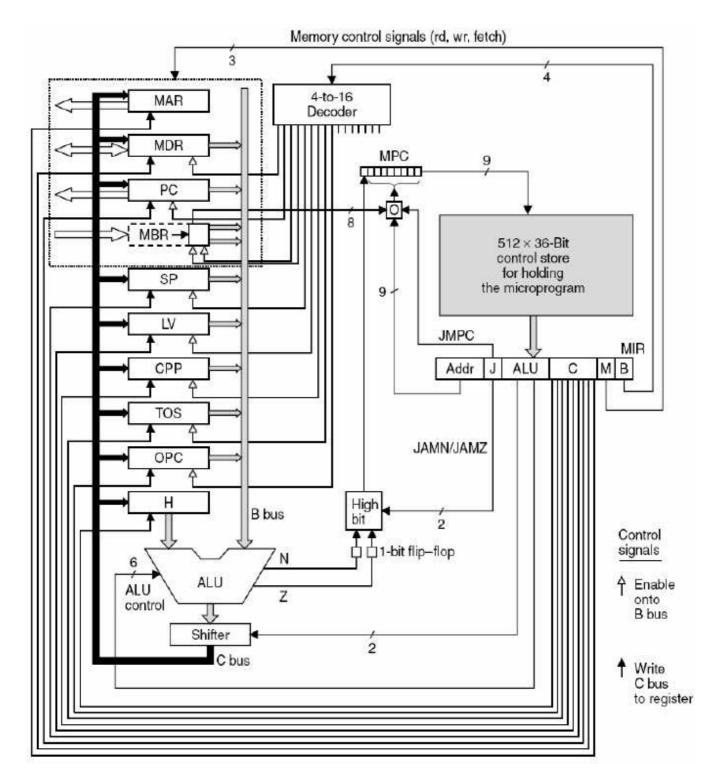

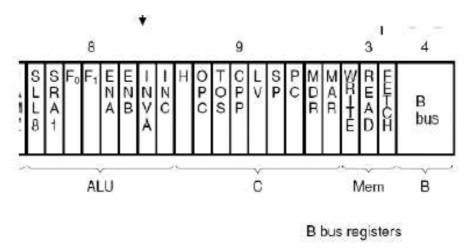

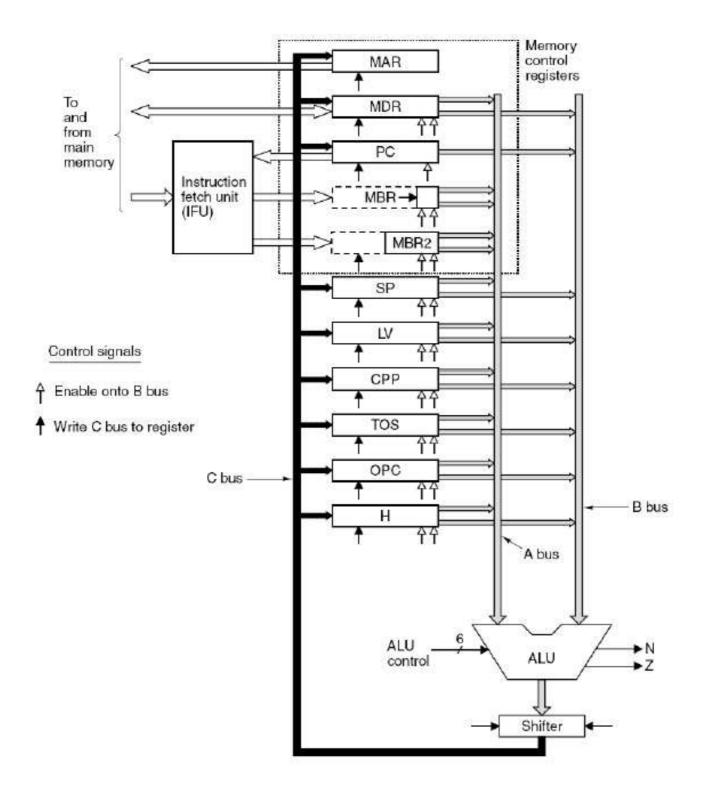

Use Figure 5, Figure 6, Figure 7 and Figure 8 for the IJVM in the appendix to answer the questions.

- a. Explain the functionality of the register "MPC".

- b. Create microinstruction(s) for the following IJVM operation: Load register "OPC" with the content of register "H".

You don't need to consider the Addr and J fields. Give the correct bit value for the ALU, C, Mem and B fields —see Figure 6.

c. Create microinstruction(s) for the following IJVM operation: TOS = LV + (OPC + 1).

You don't need to consider the Addr and J fields. Give the correct bit value for the ALU, C, Mem and B fields —see Figure 6.

## QUESTION 3: INSTRUCTION SET ARCHITECTURE LEVEL (ISA)(20%)

In an imaginary 16 bit architecture there exists only three types of instructions: Load, Store and MOVE/ALU. Figure 2 shows the format of the three instruction types.

| Load:                                                                                                                          |                                                                                                                                                                                  |                                                                                         |       |  |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|--|

| opCode                                                                                                                         | Ra                                                                                                                                                                               | Rn                                                                                      | DC    |  |

| 15                                                                                                                             |                                                                                                                                                                                  |                                                                                         | . 0   |  |

| Store:                                                                                                                         |                                                                                                                                                                                  |                                                                                         |       |  |

| opCode                                                                                                                         | Ra                                                                                                                                                                               | Rn                                                                                      | DC    |  |

| 15                                                                                                                             |                                                                                                                                                                                  |                                                                                         | 0     |  |

| Move/ ALU:                                                                                                                     |                                                                                                                                                                                  |                                                                                         |       |  |

| opCode                                                                                                                         | Ra                                                                                                                                                                               | Rb                                                                                      | Rc    |  |

| 15<br>◀───4 bit──►                                                                                                             | <b>←</b> 4 bit <b>─</b> ►                                                                                                                                                        |                                                                                         | 4 bit |  |

| Load:                                                                                                                          |                                                                                                                                                                                  |                                                                                         |       |  |

| Rn: data de<br>DC: Don't C<br>Store:<br>Ra: points t<br>Rn: data so<br>DC: Don't C<br>Move/ ALU::<br>Ra: destina<br>Rb: source | to memory location<br>estination register,<br>Care, not in use<br>to memory location<br>purce register, any<br>Care, not in use<br>tion register, any user<br>register, any user | any user register<br>n, any user register<br>user register<br>user register<br>register |       |  |

Figur 2: Possible instruction types.

- a. From the available information:

- i) What is the maximum number of instructions possible? Explain.

- ii) What is the maximum number of user registers this machine can have? Explain.

- b. What type of architecture is this instruction set for?

- c. If the format is changed for the load/store to a format using the DC field as an index for a base address in *Ra*, the addressing mode is changed. Does this change have any influence on the ISA definition for the machine? Explain.

- d. The shown machine is most likely a RISC machine. Why?

# Question 4: Computers (20% (8% on a and C; 4% on b))

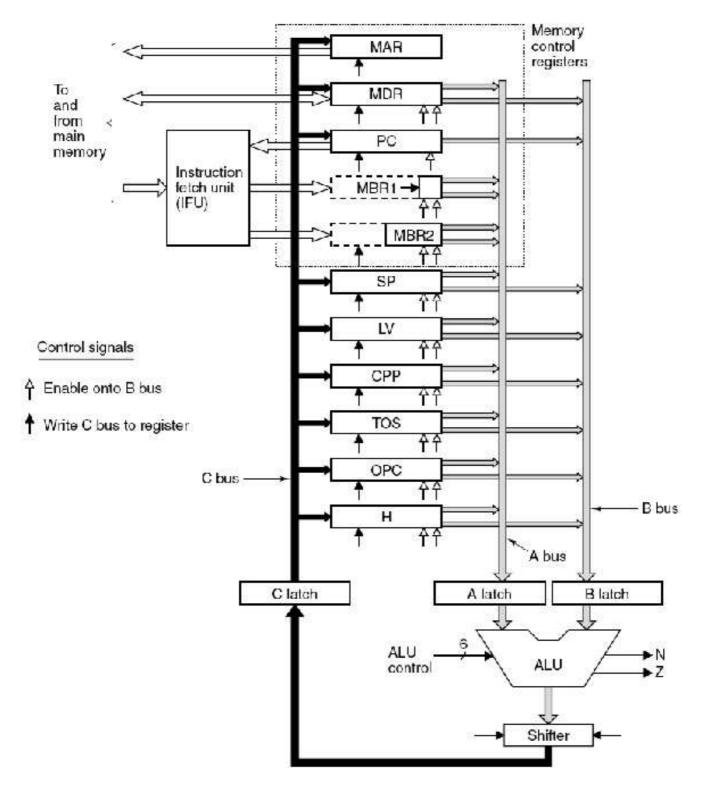

- a. Figure 9 and Figure 10 in the appendix shows different versions of the IJVM microarchitecture. What features are introduced and how does such features influence on the performance compared to the original microarchitecture shown in Figure 5?

- b. What implications do the changes in microarchitecture in question "a" have on the ISA level?

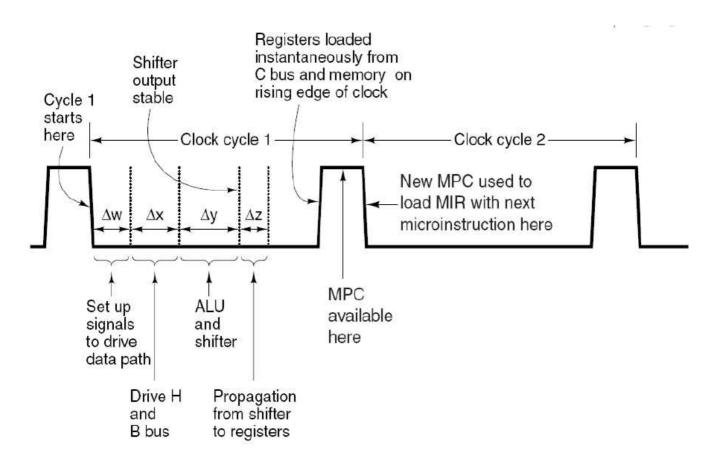

- c. See Figure 5, Figure 8 and Figure 10. Approximately, what can the clock period be reduced to if the microarchitecture is changed from the implementation shown in Figure 5 to the implementation shown in Figure 10?

### QUESTION 5: MISCELLANEOUS (20%)

Pick the right answer in the following questions. Correct answer gives 4% score, wrong answer gives -2% and don't know (no answer, more then one answer) gives 0% score.

- a. What is stored in the *Addr* field of *MIR*? See Figure 5.

- 1) The Address of the next microinstruction in *control store*.

- 2) Contains only a valid address if a conditional branch is to be executed, activation of the J bit.

- 3) At all time a copy of the content of *MBR*.

- 4) *control store* start and end address for the active microinstruction.

- b. What claim is correct for a Chip Multi Processor (CMP)?

- 1) Is an Array computer.

- 2) Is of type SIMD.

- 3) Is of type homogeneous or heterogeneous.

- 4) Is a MIMD type that always uses a crossbar for communication between the processor cores.

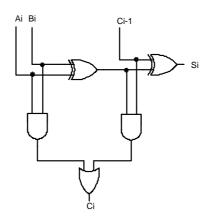

c. What is illustrated in Figur 3?

Figur 3: Mysterious device.

- 1) Full adder.

- 2) Half adder.

- 3) Static RAM cell.

- 4) Multiplexer.

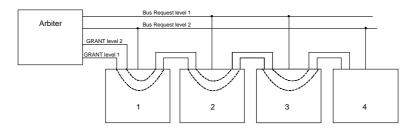

- d. What is the order of priority for the devices in Figure 4. Level 1 has higher priority then level 2. The priority is ordered from high to low.

Figur 4: Centralized bus arbiter.

- 1) 1, 2, 3, 4.

- 2) 2, 3, 1, 4.

- 3) 1, 4, 2, 3.

- 4) 3, 2, 4, 1.

- e. Which of the following claims regarding computer components is correct?

- 1) Asynchronous bus transfer must use a global clock.

- 2) An ALU that can perform addition and invert can also subtract.

- 3) EPROM and flash memory are functional equivalent.

- 4) EEPROM and flash memory are functional equivalent

IJVM appendix

Figur 5: Block diagram (IJVM).

Page 9 of 14

| 0 = MDR  | 5 = LV    |

|----------|-----------|

| 1 = PC   | 6 = CPP   |

| 2 = MBR  | 7 = TOS   |

| 3 = MBRU | 8 = OPC   |

| 4 = SP   | 9-15 none |

Figur 6: Microinstruction format (IJVM).

| Fo | F,           | ENA          | ENB     | INVA         | INC | Function  |

|----|--------------|--------------|---------|--------------|-----|-----------|

| 0  | 1            | 1            | 0       | 0            | 0   | A         |

| 0  | 1            | 0            | 1       | 0            | 0   | в         |

| 0  | ( <b>1</b> ) | 2 <b>1</b> 2 | 0       | 3 <b>1</b> 3 | 0   | A         |

| 1  | 0            | (19)<br>(19) | <u></u> | 0            | 0   | в         |

| 1  | 1            | <u> </u>     | 1       | 0            | ۵   | A + B     |

| 1  | 1            |              | 4       | 0            | 1   | A + B + 1 |

| 1  | 1            | 4            | 0       | 0            | 1   | A + 1     |

| 1  | 1            | 0            | 1       | 0            | 1   | B+1       |

| 1  | 1            | 1            | 1       | 1            | 1   | B – A     |

| 1  | 1            | 0            | 1       | 1 <b>1</b>   | 0   | B - 1     |

| 1  | 1            | - <b>1</b>   | 0       | 1            | 1   | -A        |

| 0  | <u>ः</u> 0ः  | 32           | 1       | 0            | 0   | A AND B   |

| 0  | 1            | 545          | - 1     | 0            | 0   | A OR B    |

| 0  | ٩ <u>ب</u>   | 0            | 0       | 0            | 0   | 0         |

| 1  | 1            | 0            | 0       | 0            | 1   | 1         |

| 1  | 1            | 0            | 0       | 1            | 0   | -10       |

SLR1 SLL8 Function

0 0 No shift

0 1 Shift 8 bit left

1 0 Shift 1 bit right

Figur 7: ALU functions (IJVM).

Figur 8: Timing diagram (IJVM).

Figur 9: Alternative microarchitecture I.

Page 13 of 14

Figur 10: Alternative microarchitecture II.

Page 14 of 14